デジタル シミュレーション入門¶

Qucsは、デジタルシミュレーションを実行するグラフィカルユーザインタフェースでもあります。この文書では、それをどのように使うことができるかを少し説明します。

For digital simulations Qucs uses the FreeHDL program (http://www.freehdl.seul.org). So the FreeHDL package as well as the GNU C++ compiler must be installed on the computer.

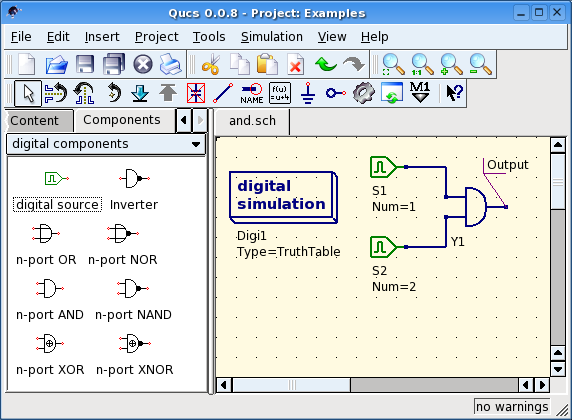

There is no big difference in running an analog or a digital simulation. So having read the Getting Started for analog simulations, it is now easy to get a digital simulation work. Let us compute the truth table of a simple logical AND cell. Select the digital components in the combobox of the components tab on the left-hand side and build the circuit shown in figure 1. The digital simulation block can be found among the other simulation blocks.

デジタルソース S1 と S2 は入力で、 Output というラベルのついたノードが出力です。シミュレーション実行後、データディスプレイのページが開きます。t truth table という図表をその上に配置して、 Output という変数を挿入しましょう。そうすると、2ポートANDセルの真理値表が表示されます。おめでとうございます、最初のデジタルシミュレーションは終了です。

図1 - Qucsのメインウィンドウ

Qucsで出来るデジタルシミュレーションは、真理値表だけではありません。回路に任意の信号を印加し、タイミング図に出力信号を観測することもできます。それを行うには、シミュレーションブロックの Type というパラメータは、 TimeList に変更されなくてはなりませんし、次のパラメータとしてシミュレーションの期間が入力されなくてはなりません。デジタルソースは、ここでは別の意味を持ちます:それらは、最初のビット(ローかハイか)と状態が変化する時刻のリストを定義することで、任意のビット系列を出力できます。このリストは、終了後も繰り返すことに注意してください。そのため、パルス比が1:1の1GHzのクロックを作るには、リストは、0.5ns;0.5nsとなります。

この種のシミュレーション結果を表示するために、 timing diagram という図表が用意されています。ここで、すべての出力ノードは、1つの図表の行ごとに表示されます。では、どうぞ楽しんでください。

VHDL File Component¶

より複雑で、より普遍的なシミュレーションは、”VHDL file”という部品を使って実行できます。この部品は、部品のリストビュー(”digital components”のセクション)から選択できます。そうはいったものの、お薦めの使い方は以下の通りです:そのVHDLファイルは、プロジェクトのメンバーである必要があります。そのうえで、コンテンツリストビューに移動し、ファイル名をクリックしてください。回路図の領域に入った後、VHDL部品を配置することができます。

VHDLファイルの最後の実体ブロックは、インターフェイスを定義します。すなわち、すべての入力および出力ポートはここで宣言されなければなりません。これらのポートはまた、回路図シンボルで示されており、回路の残りの部分に接続することができます。シミュレーションの最中にVHDLファイルのソースコードは、トップレベルのVHDLファイル内に配置されます。これにはいくつかの制限が 伴うので、考慮に入れなければなりません。例えば、VHDLファイル内のエンティティ名は、すでにサブサーキットに与えられた名前と異なる必要があります。 (シミュレーションの後、完全なソースコードは、F6キーを押すことで見ることができます。この手順の感覚を身につけるために、やってみてください。)