Швидкий старт в цифровому моделюванні¶

Qucs - надає також графічний інтерфейс користувачу для виконання цифрового моделювання. Даний документ коротенько описує, як для цього користовуватись Qucs.

For digital simulations Qucs uses the FreeHDL program (http://www.freehdl.seul.org). So the FreeHDL package as well as the GNU C++ compiler must be installed on the computer.

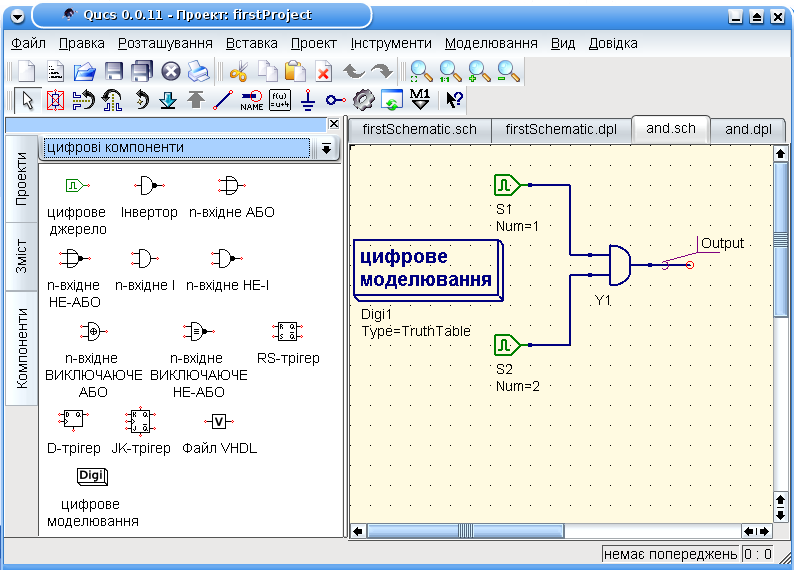

There is no big difference in running an analog or a digital simulation. So having read the Getting Started for analog simulations, it is now easy to get a digital simulation work. Let us compute the truth table of a simple logical AND cell. Select the digital components in the combobox of the components tab on the left-hand side and build the circuit shown in figure 1. The digital simulation block can be found among the other simulation blocks.

Цифрові джерела S1 і S2 підключені до входів, вузол з міткою Output є виходом. Після виконання моделювання відкривається сторінка показу даних. Помістіть на неї діаграму Таблиця істинності і вставте зміну Output. Тепер показується таблиця істинності дво-вхідного елемента І. Поздоровлення, перше цифрове моделювання зроблено!

Мал. 1 - Головне вікно Qucs

Таблиця істинності - далеко не єдиний вид моделювання, котрий можна виконати в Qucs. Можливо також подати на вхід випадковий сигнал і подивитися вихідний сигнал в часовій діаграмі. Для цього, треба поміняти параметр Type блоку моделювання на TimeList і у наступному параметрі слід ввести тривалість моделювання. Тепер в цифрових джерел інший зміст: вони можуть видавати випадкову послідовність бітів, для цього їм потрібно вказати перший біт (низький чи високий) і список моментів часу наступної зміни стану. Зверніть увагу, що цей перелік повторюється після кінця. Тому, щоб отримати тактові імпульси з частотою 1 ГГц і скважністью 1:1, у списку має бути записано: 0.5ns; 0.5ns.

Для відображення результатів цього моделювання є часова діаграма. У ній результати всіх вихідних сигналів можуть бути зображені пострічково в одній діаграмі. Отож успіхів у цій справі...

Файловий компонент VHDL¶

Більш складні і більш універсальні види моделювання можуть бути виконані з допомогою компонента “файл VHDL”. Цей компонент можна взятий з списку компонентів (розділ “цифрові компоненти”). Проте, рекомендується наступний спосіб: файл VHDL повинен бути в складі проекту. Потім перейдіть в перегляд вмісту проекту й натисніть ім’я файла. Зайшовши у область побудови схем, помістіть компонент VHDL.

Останній об’єктний блок в файлі VHDL визначає інтерфейс, тобто тут повинні бути оголошені всі вхідні і вихідні виводи. Такі виводи показуються також на схемному позначенні і можуть бути з’єднані з іншою схемою. Під час моделювання вихідний код файла VHDL поміститься у VHDL-файл верхнього рівня. Це треба враховувати, оскільки це веде до деяких обмежень. Наприклад, імена об’єктів у VHDL-файлі мають відрізнятись від іменам, вже даних підсхемам. (Після моделювання повний вихідний код можна переглянути, натиснувши F6. Користуйтеся цим, щоб відчути процес.)