Začínáme s Digitálními sumulacemi¶

Qucs obsahuje také grafické rozhraní umožňující digitální simulace. Tento manuál by vám měl ukázat “Jak nato”.

For digital simulations Qucs uses the FreeHDL program (http://www.freehdl.seul.org). So the FreeHDL package as well as the GNU C++ compiler must be installed on the computer.

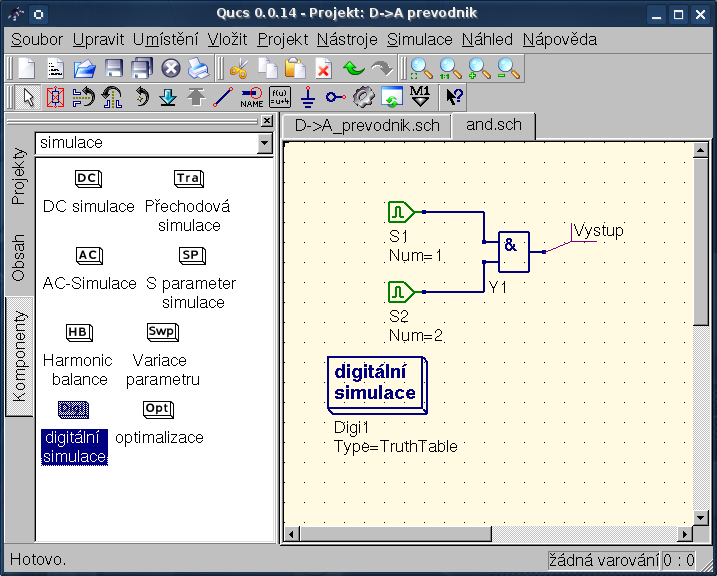

There is no big difference in running an analog or a digital simulation. So having read the Getting Started for analog simulations, it is now easy to get a digital simulation work. Let us compute the truth table of a simple logical AND cell. Select the digital components in the combobox of the components tab on the left-hand side and build the circuit shown in figure 1. The digital simulation block can be found among the other simulation blocks.

Digitální zdroje S1 a S2 jsou vstupy. Uzel nadepsaný jako Output je výstup. Po provedení simulace se otevře okno, ve kterém se vypisují data ze simulace. Umístěte diagram Logická tabulka (Pradivostní tabulka). Vyberte proměnnout Output. Nyní se nám zobrazí pravdivostní tabulka dvou-vstupového hradla AND. Gratuluji, první digitální simulace je hotová!

Obrázek 1 - Qucs - hlavní okno

Pravdivostní tabluka není jediné, co Qucs zvládne. Je zde také možnost poslat náhodný signál do obvodu a podívat se na na výstup v časovém diagramu. Pro to ale musíme změnit parametr simulace. Vraťte se ke schématu a změňte v Type (stačí jednou kliknout) TruthTable na TimeList. Nebo jednodušeji dvakrát klikněte na ikonu “Digitální simulace” a zde změňte “TruthTable” na “TimeList”. Ale během simulace musí být zadán další parametr. Digitální zdroje se nyní chovají jinak. Na jejich výstupech se náhodně mění sekvence bitů od prvního (definovaného) bitu (logická “0” nebo logická “1”). Dále je třeba nastavit seznam, kerý bude určovat kdy se bude měnit jejich logické stavy. Po “přečtení” tohoto seznamu se “přečte” ještě jednou a pak se program ukončí. Takže vytvořme generátor s taktovací frekvencí 1GHz se střídou 1:1, do listu se zapíše: 0.5ns, 0.5ns

Pro zobrazení výsledků typu této simualce je zde navržený diagram Časový diagram. Zde mohou býte zobrazeny výsledky všech výstupů za sebou na řádkách. Takže, teď si můžete hrát ;-)

Komponenta VHDL soubor¶

Více složité a více univerzální simulace mohou být zrealizovány použitím komponenty “VHDL soubor”. Tuto komponentu můžete najít v skupině komponent “Digitální komponenty”. Přesto je však doporučeno, že VHDL soubor by měl být součástí projektu. Vraťte se zpět na “Obsah” a kllikněte na název souboru. Po “vstupu” do schématu by se měla komponenta VHDL vložit

Poslední část ve VHDL souboru definuje prostředí, to jsou všechny vstupy a mýstupy. Ty také musejí být deklarovány právě zde. Kontakty jsou rovněž ve schématu a mohou být propojeny se zbytkem obvodu. Během simulace je zdrojový kód VHDL souboru umístěn do nejvyšší úrovně VHDL souboru. Toto musí být šetrné kvůli jistým limitacím. Například celky názvů ve VHDL souboru musí být různé než jsou názvy vnořených obvodů. Po simulaci můžete zobrazit kompletní zdrojový kód stisknutím klávesy F6. Zobrazte si jej pokud se chcete o této proceduře dozvědět více.